- News

5 November 2013

Imec demos first III-V FinFET devices monolithically integrated on 300mm silicon

By using a unique silicon fin replacement process, Imec of Leuven, Belgium has demonstrated what it claims are the first III-V compound semiconductor FinFET devices integrated epitaxially on 300mm silicon wafers.

The nanoelectronics research center says that the achievement illustrates progress toward high-volume manufacturing on 300mm and future 450mm wafers of advanced heterogeneous CMOS devices, monolithically integrating high-density compound semiconductors on silicon. The development not only enables continual CMOS scaling down to 7nm and below, but also enables new heterogeneous system opportunities in hybrid CMOS-RF and CMOS-optoelectronics, imec adds.

“To our knowledge, this is the world’s first functioning CMOS-compatible III-V FinFET device processed on 300mm wafers,” says An Steegen, senior VP core CMOS at imec, “demonstrating the technology as a viable next-generation alternative for the current state-of-the-art Si-based FinFET technology in high volume production.”

The proliferation of smart mobile devices and the ever growing user expectations for bandwidth and connectivity will drive the continual need for software and hardware advances extending from networks to data servers and mobile gadgets, says imec. At the core of the hardware will be new process technologies that allow more power-efficient CMOS transistors and increased integration, enabling a higher level of functionality. This prompts process technologies that enable heterogeneous devices spanning operating ranges for targeted circuits, maximizing system performance.

“During the last decade, transistor scaling has been marked by several leaps in process technologies to provide performance and power improvements,” notes imec’s director of the logic R&D Aaron Thean. “The replacement of poly-silicon gate by high-k metal-gate in 45nm CMOS technology in 2007 represented a major inflection in new material integration for the transistor. The ability to combine scaled non-silicon and silicon devices might be the next dramatic transistor face-lift, breaking almost 50 years of all-silicon reign over digital CMOS,” he adds. “This work represents an important enabling step towards this new paradigm.”

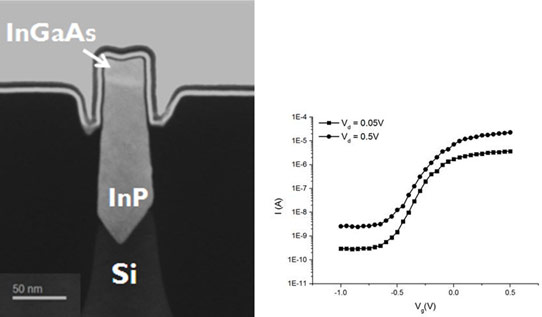

Picture: FinFET structure (with InGaAs and InP replacing silicon) and I-V characteristics.

At the finest grain, co-integration of high-density heterogeneous transistors has been challenged by the ability to combine disparate materials and structures while maintaining low enough complexity and defectivity. Imec’s new process selectively replaces silicon fins with indium gallium arsenide (InGaAs) and indium phospide (InP), accommodating close to 8% of atomic lattice mismatch. The new technique is based on aspect-ratio trapping of crystal defects, trench structure, and epitaxial process innovations. The resulting FinFET device integrating III-Vs on silicon shows what is claimed to be excellent performance.

Imec’s research into next-generation FinFETs is performed as part of its core CMOS program, in cooperation with key partners including Intel, Samsung, TSMC, Globalfoundries, Micron, SK Hynix, Toshiba, Panasonic, Sony, Qualcomm, Altera, Fujitsu, nVidia, and Xilinx.